### Desain dan Analisis *Inverter* Tiga Fasa untuk Aplikasi Sistem PLTS Terhubung Grid PLN sebagai Referensi

M. Yasin\*<sup>1</sup>, Faizal Arya Samman<sup>1</sup>, Rhiza S.Sadjad<sup>1</sup>

<sup>1</sup>Teknik Elektro, Fakultas Teknik, Universitas Hasanuddin Makassar Jl. Perintis Kemerdekaan Km. 10, Tamalanrea Indah, Makassar, \*Email: ysn\_sw77@yahoo.com

#### Abstrak

Paper ini memperlihatkan hasil simulasi dan analisis *inverter* tiga-fasa yang akan digunakan pada sistem pembangkitan listrik tenaga surya, yang berfungsi mengubah sumber arus searah dari panel surya menjadi arus bolak-balik. Dalam simulasi, *inverter* dimodelkan dan didesain dengan menggunakan tegangan referensi dari jala-jala PLN sebagai acuan untuk membangkitkan sinyal kendali PWM (*Pulse Width Modulation*). Sinyal PWM ini dikirimkan ke pintu gate dari komponen saklar transistor daya, yang dalam hal ini digunakan IGBT (*Insulated Gate Bipolar Transistor*). Pengaturan irama penyaklaran akan mengubah sumber tegangan DC (*Direct Current*) menjadi tegangan AC (*Alternating Current*). Dengan menggunakan filter pasif LC, maka sinyal keluaran dari *inverter* dapat diubah menjadi gelombang sinusoidal berfrekuensi 50Hz sebagaimana diharapkan. *Output* sinyal *inverter* terhadap PLN memiliki perbedaan fasa sehingga disimulasikan sebuah mekanisme yang dapat mendeteksi beda fasa dan mengatur delay pwm sehingga *output inverter* dan sefasa dengan PLN. Hasil analisis menunjukkan bahwa tegangan fasa dan beda fasa dari keluaran *inverter* dapat diatur sesuai dengan tegangan pada fasa grid PLN.

#### Abstract

This paper shows the results of simulations and analysis of three-phase *inverters* to be used in solar power generation systems, which function to convert the direct current source from the solar panel into alternating current. In the simulation, the *inverter* is modeled and designed using the reference voltage of the PLN mesh as a reference to generate the PWM (Pulse Width Modulation) control signal. This PWM signal is sent to the gate door of the switch component of the power transistor, which in this case is used IGBT (Insulated Gate Bipolar Transistor). The switching cadence setting changes the DC Current (Direct Current) source to AC voltage (Alternating Current). By using LC passive filter, the *output* signal from the *inverter* can be converted into 50Hz frequency sinusoidal wave as expected. The *output* of the *inverter* signal to the PLN has a phase difference so that it is simulated a mechanism that can detect the phase difference and adjust the pwm delay so that the *inverter* and in phase *output* with PLN. The results of the analysis show that the phase and phase voltages of the *inverter output* can be adjusted according to the voltage on the PLN grid phase.

Kata- Kunci: Inverter 3 Fasa, Grid PLN, IGBT, PWM.

#### 1. Pendahuluan

Saat ini sumber energi yang paling banyak digunakan di dunia adalah energi fosil yang berupa bahan bakar minyak. Energi fosil adalah energi yang tak terbarukan dan akan habis pada beberapa tahun yang akan datang [1]. Energi alternatif merupakan solusi untuk mengganti kebutuhan akan energi fosil. Misalnya panas bumi, biomassa, sinar matahari, nuklir, dan sebagainya.

Kebutuhan energi listrik yang terus meningkat berpotensi menghasilkan *overloads* jaringan distribusi yang menciptakan masalah seperti pemadaman, ketidakstabilan grid, penurunan kualitas daya, keamanan daya dan sebagainya. Untuk menyeimbangkan kebutuhan energi, maka diperlukan pembangkit daya baru dan terbarukan seperti *Photovoltaic* (PV), Angin, dan Biomassa [2].

Piranti-piranti yang menghasilkan energi baru dan terbarukan misalnya saja sel surya menghasilkan tegangan dalam bentuk DC. Sehingga dibutuhkan sebuah *inverter* tegangan arus DC ke AC agar dapat di gunakan oleh peralatan listrik rumah tangga [3].

Untuk menyalurkan daya keluaran *inverter* yang bersumber dari PLTS dengan jaringan listrik dibutuhkan proses sinkronisasi dengan cara mengontrol kerja *inverter* sedemikian rupa sehingga diperoleh tegangan, amplitodo sesaat, fase dan frekuensi yang sesuai dengan jaringan listrik. Pengaturan sistem sinkronisasi dan pembentuk gelombang keluaran dilakukan dengan tegangan jaringan sebagai acuan.

Bila tegangan jaringan turun, maka tegangan *inverter* juga harus mengikuti, begitu sebaliknya. Demikian pula bila frekuensi jaringan listrik naik atau turun, maka frekuensi keluaran *inverter* juga harus dapat mengikutinya.

### 2. Deskripsi Permasalahan

Dalam tahap interkoneksi, masalah yang dihadapi adalah harmonisa keluaran inverter dan sinkronisasi fasa frekuensi tegangan keluaran inverter dan grid. Bila karakteristik daya listrik dihasilkan inverter tidak sinkron, yang dimungkinkan pengoperasian paralel akan mengakibatkan ketidakstabilan dan bahkan kegagalan pada jaringan distribusi. Sedangkan harmonisa atau masalah ketidakmurnian isyarat tegangan pada keluaran inverter akan berpengaruh kondisi ketahanan peralatan/perangkat listrik lainnya.

Paper ini akan memberikan suatu mekanisme sinkronisasi koneksi tegangan keluaran *inverter* dengan tegangan pada jaringan listrik PLN, dengan *Total Harmonik Distortion* (THD) yang sangat rendah. Sehingga didapatkan desain *inverter on grid* 3 fasa yang mampu mengubah arus DC menjadi arus AC kemudian menyalurkannya ke jaringan listrik utilitas (PLN).

Sebelumnya dilakukan simulasi model DC-AC *converter* untuk menemukan nilai komponen yang akan di gunakan pada modul *inverter*.

### 3. Hasil Perancangan

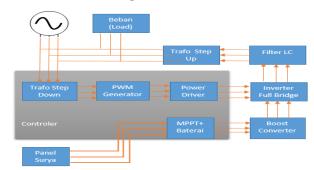

Gambar 1. Rancangan panel surya terhubung grid

### 3.1. Rangkaian Inverter tiga fasa dengan Pspice

Pada rangkaian *inverter* tiga fasa tanpa filter digunakan parameter-parameter seperti terlihat dalam Tabel berikut:

Tabel 1: Parameter SimulasiNama ParameterStatusV input220 volt DCV jala-jala (grid)380 volt ACRa, Rb, Rc (beban Rload)50 ohmLa, Lb, Lc (beban Lload)5 mHSwitchIGBT

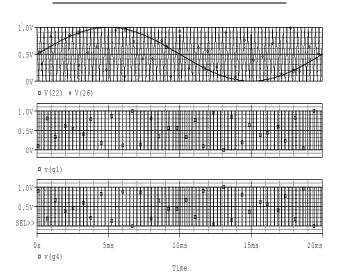

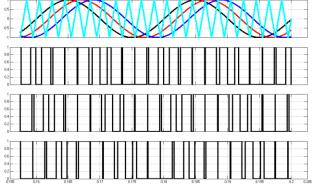

Gambar 2. Sinyal PWM yang dibangkitkan untuk gate 1 - 4

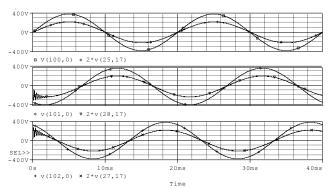

Gambar 2 merupakan hasil simulasi dari rangkaian *inverter* tanpa filter dimana gambar plot pada baris pertama menggambarkan input sinusoidal dari jala-jala PLN tiga fasa. Gambar plot pada baris kedua mengambarkan hasil keluaran dari *inverter* tanpa filter untuk fasa A. Gambar plot baris ketiga untuk fasa B dan untuk yang ke empat merupakan fasa C dari *output*

*inverter*. Hasil simulasi memperlihatkan *output* keluaran mengikuti fasa input dari PLN tiap fase keluaran dari *inverter*.

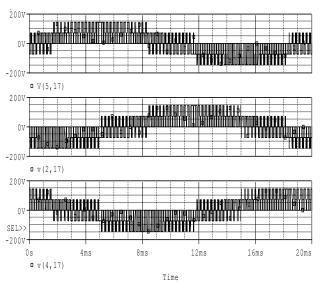

Hasil simulasi dari rangkaian inverter dengan menggunakan filter dapat dilihat pada Gambar 4 Dalam simulasi digunakan filter LC dengan nilai komponen L sebesar 5mH dan nilai C adalah 1 uF untuk masing-masing beban yang terhubung setiap fase ke ground. Hasil simulasi memperlihatkan pergeseran fasa sesuai dengan referensi input dari jala-jala PLN tetapi terdapat beberapa ketidak stabilan pada tegangan dengan penurunan tegangan input dari 50 volt tegangan input DC menjadi kurang lebih 30 volt tegangan output AC pada keluaran inveter yang telah di beri filter LC.

Gambar 3.Sinyal *output inverter* tanpa filter untuk fasa R, S dan T

Filter yang digunakan adalah filter jenis LC. Komponen L ditambahakan pada tiap-tiap terminal fasa keluaran untuk mengoreksi nilai induktif pada beban RL yang sudah terpasang sebelumnya. Komponen kapasitor digunakan untuk memfilter riak yang dihasilkan dari tegangan keluaran.

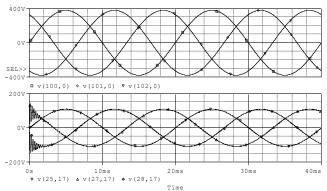

Gambar 4. Sinyal *output inverter* dengan filter untuk fasa R, S dan T

Gambar 4 memperlihatkan hasil simulasi rangkaian dengan menggunakan filter LC. Gambar baris atas memperlihatkan tegangan untuk setiap 3 fasa dari jala-jala (grid). Pada bagian bawah, terlihat tegangan keluaran *inverter* untuk masing-masing ketiga fasanya. Pada saat awal, nampak terlihat kondisi peralihan tegangan keluaran yang berlangung kira-kira 2 millidetik.

Gambar 5. Perbandingan sinyal PLN dengan *output* inverter

Gambar 5 memperlihatkan grafik perbandingan langsung antara tegangan jala-jala dengan keluaran inverter untuk setiap fasanya. Nampak terlihat bahwa tegangan keluaran inverter mengalami degradasi sehingga keluarannya hanya berkisar lebih besar sedikit dari 100V. Grafik keluaran inverter pada Gambar 9 diperbesar dua kali untuk melihat lebih jelas perbedaan fasa antara kedua tegangan tadi. Keluaran inverter dapat diperbesar dengan menggunakan misalnya trafo penaik tegangan.

## 3.2. Mekanisme Sinkronisasi *Inverter* Terhadap Grid PLN

Proses perancangan mekanisme interkoneksi tidak menitikberatkan pada teori matematis tetapi lebih ke arah perancangan sistem digital agar dapat diterapkan langsung ke *device* FPGA.

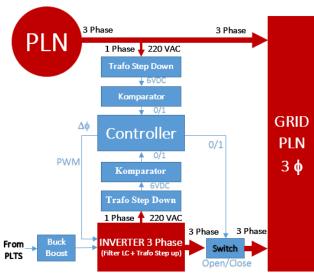

Adapun rancangan mekanisme untuk sinkronisasi adalah sebagai berikut :

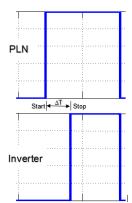

a. Proses Sampling: salah satu fasa dari tegangan Listrik PLN (misal fasa R) akan diturunkan oleh trafo *step down* dari 220 VAC menjadi 6 VAC. Begitu juga pada salah satu fasa dari tegangan *inverter* (misal fasa R) akan diturunkan juga oleh trafo *Step down* dari 220 VAC menjadi 6 VAC. Tegangan *output* trafo *step down* 6VAC akan dibandingkan terhadap titik nol oleh komparator jika tegangan sesaat lebih besar nol maka komparator berlogika *High* dan jika nilai tegangan sesaat lebih kecil atau sama dengan nol maka komparator berlogika *Low*.

Gambar 6. Mekanisme sinkronisasi interkoneksi inverter dengan grid PLN

b. Proses Deteksi Beda Fasa: Logika tegangan dari komparator di sisi PLN dan komparator di sisi *Inverter* akan menjadi input oleh *controller* dan diolah sehingga mengeluarkan *output* berupa nilai beda fasa antara sinyal *output Inverter* dengan sinyal PLN. Nilai beda fasa dapat diperoleh dengan menghitung rentang waktu dimulai saat sinyal PLN terbaca dari nilai dibawah nol ke nilai di atas nol dan diakhiri saat sinyal *output inverter* terbaca dari

- nilai dibawah nol ke nilai di atas nol. Rentang waktu tersebut akan dibagi dengan periode 20 ms (Frekuensi 50 Hz) dan hasilnya akan dikalikan dengan 360°. jika didapatkan sudut lebih besar dari 180° maka nilai sudut tersebut akan dikonversi ke sudut di bawah 180° dengan arah pergeseran *lagging* ke *leading*.

- c. Proses Switching dan Sinkronisasi: Nilai beda fasa yang didapatkan oleh controller akan menentukan waktu delay pada PWM yang akan mengatur proses switching pada IGBT yang ada pada inverter tiga fasa. Sinyal hasil switching oleh IGBT akan difilter oleh filter LC sehingga didapatkan sinyal sinusoidal. Proses delay pada PWM berfungsi sebagai sinkronisasi fasa inverter terhadap PLN. Jika telah terjadi sinkronisasi dimana nilai beda fasa yang didapatkan masih berada dalam batas toleransi maka controller akan menutup switch sehingga sinyal output inverter tiga fasa dapat terkoneksi dengan Grid PLN. Jika belum sinkron maka controller akan membuka Switch

#### 4. Hasil Simulasi

4.1. Pengujian Data Sampling Pembuatan Sinyal PWM

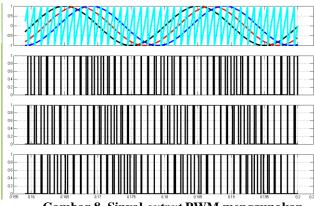

Sinyal PWM satu periode setara dengan frekuensi PLN 50 HZ atau T = 20 ms dibuat dengan membandingkan sinyal sinusoidal terhadap sinyal segitiga.

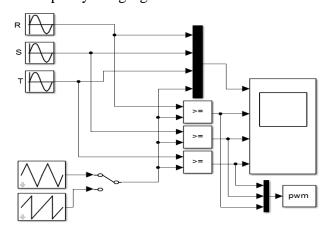

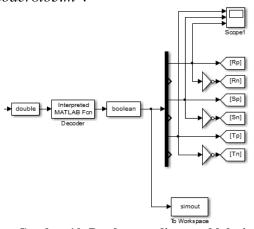

Gambar 7.Simulasi deteksi beda fasa sinyal *inverter* dengan grid PLN

Gambar 8. Sinyal *output* PWM menggunakan sawtooth

Dari Gambar 7 digunakan blok "to workspace" yang berfungsi untuk mengirim sinyal hasil simulasi PWM ke command window. Data PWM hasil simulasi sesuai Gambar 8 atau Gambar 9 dengan ukuran data sebesar 2331 x 3 yang artinya ada tiga sinyal PWM yakni untuk fasa R, S dan T dengan masing-masing sinyal berjumlah 2331 data.

Gambar 9. Sinyal output PWM menggunakan triangle

## 4.2. Pengujian Data Kuantisasi PWM dengan Data Biner 8 bit

Tabel 2 : Hasil pengujian data PWM yang telah dikuantisasi menggunakan *Counter* Triangle

| Counter<br>Triangle | PWM Signal |    |    | - Decoder | Sudut Fasa |

|---------------------|------------|----|----|-----------|------------|

|                     | G1         | G3 | G5 | - Decouer | Sudut Fasa |

| 0                   | 0          | 1  | 1  | 3         | 0.00       |

| 1                   | 0          | 1  | 1  | 3         | 1.41       |

| 2                   | 0          | 1  | 1  | 3         | 2.82       |

| 3                   | 0          | 1  | 1  | 3         | 4.24       |

| 4                   | 0          | 1  | 1  | 3         | 5.65       |

| 5                   | 0          | 1  | 1  | 3         | 7.06       |

| 6                   | 0          | 1  | 1  | 3         | 8.47       |

| 7                   | 0          | 1  | 0  | 2         | 9.88       |

| 8                   | 0          | 1  | 0  | 2         | 11.29      |

| 9                   | 0          | 1  | 0  | 2         | 12.71      |

| Counter<br>Triangle | PWM Signal |    |    | Danadan   | Sudut Fasa |

|---------------------|------------|----|----|-----------|------------|

|                     | G1         | G3 | G5 | - Decoder | Sudut Fasa |

| 10                  | 0          | 1  | 0  | 2         | 14.12      |

| 11                  | 0          | 1  | 0  | 2         | 15.53      |

| 12                  | 0          | 1  | 0  | 2         | 16.94      |

| 13                  | 0          | 1  | 0  | 2         | 18.35      |

| 14                  | 0          | 1  | 0  | 2         | 19.76      |

| 15                  | 0          | 1  | 0  | 2         | 21.18      |

| 16                  | 0          | 1  | 0  | 2         | 22.59      |

| 17                  | 0          | 1  | 0  | 2         | 24.00      |

| 18                  | 1          | 1  | 0  | 6         | 25.41      |

| 19                  | 1          | 1  | 0  | 6         | 26.82      |

| 20                  | 1          | 1  | 0  | 6         | 28.24      |

Untuk menyederhanakan jumlah data PWM yang telah diuji pada tahap sebelumnya, maka data tersebut dikompres dengan metode interpolasi cubic menggunakan perintah Interpl seperti :

"pwmr=interp1(tout',double(pwm(:,1))',t','cubic');"

Dimana tout adalah jumlah data untuk waktu simulasi dan t adalah waktu pwm yang telah dikompress menjadi 256 data dengan menggunakan perintah

"t = linspace(0,0.02,256);"

Tabel 3 : Hasil pengujian data PWM yang telah dikuantisasi menggunakan *Counter* Sawtooth

| Counter<br>Sawtooth | PWM Signal |    |    | D I     | C1-4 E     |

|---------------------|------------|----|----|---------|------------|

|                     | G1         | G3 | G5 | Decoder | Sudut Fasa |

| 0                   | 1          | 1  | 0  | 6       | 0.00       |

| 1                   | 1          | 1  | 0  | 6       | 1.41       |

| 2                   | 1          | 1  | 0  | 6       | 2.82       |

| 3                   | 1          | 1  | 0  | 6       | 4.24       |

| 4                   | 1          | 1  | 0  | 6       | 5.65       |

| 5                   | 1          | 1  | 0  | 6       | 7.06       |

| 6                   | 1          | 1  | 0  | 6       | 8.47       |

| 7                   | 1          | 1  | 1  | 7       | 9.88       |

| 8                   | 1          | 1  | 1  | 7       | 11.29      |

| 9                   | 1          | 1  | 1  | 7       | 12.71      |

| 10                  | 1          | 0  | 0  | 4       | 14.12      |

| 11                  | 1          | 0  | 0  | 4       | 15.53      |

| 12                  | 1          | 0  | 0  | 4       | 16.94      |

| 13                  | 1          | 0  | 0  | 4       | 18.35      |

| 14                  | 1          | 0  | 0  | 4       | 19.76      |

| 15                  | 1          | 0  | 0  | 4       | 21.18      |

| 16                  | 1          | 1  | 0  | 6       | 22.59      |

| 17                  | 0          | 1  | 0  | 2       | 24.00      |

| 18                  | 0          | 1  | 0  | 2       | 25.41      |

| 19                  | 0          | 1  | 0  | 2       | 26.82      |

| 20                  | 0          | 1  | 0  | 2       | 28.24      |

Dengan memilih jumlah data PWM sebanyak 256 data maka dibutuhkan delapan buah flip-flop  $(256=2^8)$  agar dapat mencacah dari 0 hingga 255 hitungan. Pencacahan *counter* dari 0 hingga 255 hitungan akan setara dengan sebuah sinyal sinusoidal dengan fasa R dari  $0^0$  hingga  $360^0$ . Fasa R, S dan T akan berbeda  $120^0$  atau setara dengan 85 cacahan.

# 4.3. Pengujian Pembuatan PWM Generator Berbasis FPGA

Dengan mengacu pada Tabel 2 dan 3 yang ada pada tahap sebelumnya maka dapat dilihat bahwa sinyal PWM untuk fasa R, S dan T bergeser 85 cacahan atau setara dengan 120°. Jika nilai biner dari sinyal PWM untuk fasa R, S dan T dikonversi menjadi nilai cacahan, maka akan didapatkan urutan nilai cacahan tiga bit yang tidak berurutan yang terdiri atas nilai nol hingga tujuh.

Nilai cacahan tiga bit yang tidak berurutan sebanyak 256 kali dapat dibuat dengan membuat decoder 8 to 3 dengan kombinasi tabel kebenaran dapat dilihat kembali pada Tabel 2 proses pembuatan decoder dapat melalui proses penyederhanaan K-map (Karnough map) sehingga didapatkan persamaan aljabar boolean untuk nilai R, S dan T kemudian dapat dirangkaian kombinasi gerbang-gerbang logika. Jika decoder diterapkan pada FPGA maka proses pembuatan decoder dapat diganti dengan instruksi penyeleksian seperti yang dapat dilihat pada lampiran "Listing Program Matlab decoder8to3.m".

Gambar 10. Pembuatan diagram blok simulink untuk decoder PWM

# 4.4. Pengembangan Controller pada Mekanisme Sinkronisasi *Inverter* terhadap Grid PLN

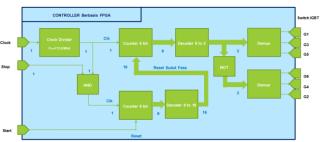

Nilai *clock* pada *Controller* FPGA akan disesuaikan oleh sub sistem *Clock Divider* sehingga frekuensi *clock* yang masuk ke *counter* akan bernilai 12.8 MHz. *Counter* 8 bit, *Decoder* 8 to 3 dan Demux (demultiplexer) akan membentuk sebuah sub sistem "PWM *generator*" yang berfungsi untuk mengirimkan sinyal *switching* pada enam buah komponen IGBT.

Counter 8 bit dan Decoder 8 to 16 akan membentuk sebuah Sub sistem "Phase Detector" dimana sinyal Start sebagai pengatur reset counter akan didapatkan dari output Komparator dari sinyal Grid PLN. Sedangkan sinyal Stop sebagai pengatur pintu masuk sinyal clock pada counter akan didapatkan dari output komparator dari sinyal Inverter. Masing-masing sinyal dari grid PLN maupun dari inverter akan diturunkan terlebih dahulu oleh trafo step down sebelum masuk ke komparator.

Gambar 11. Rancangan controller untuk sinkronisasi inverter terhadap grid PLN

Gambar 12. Perhitungan waktu beda fasa antara PLN dengan *inverter*

Sub sistem PWM generator berupa *clock*, *Counter* 8 bit dan *Decoder* 8 to 3 telah berhasil disimulasikan pada laporan penelitian ini. Untuk sub sistem *Phase Detector* berupa *Counter* 8 bit

dan *Decoder* 8 to 16 masih berupa rancangan yang dapat dikembangkan lebih lanjut. Nilai ΔT yang didapatkan dari hitungan *Counter* 8 bit dapat diketahui nilai beda fasanya dengan melihat Tabel 2 dan 3 pada tahap pengujian sebelumnya. Nilai *counter* hasil perhitungan tersebut akan diubah oleh *decoder* 8 to 16 menjadi sinyal bit Set delapan bit. Kombinasi sinyal bit Set dan Reset untuk masingmasing flip-flop yang ada di PWM *generator*.

### 5. Kesimpulan

Mekanisme sinkronisasi koneksi tegangan keluaran *inverter* dengan tegangan pada jaringan listrik PLN telah dirancang dan sebagian telah diuji coba menggunakan matlab simulink dengan

hasil pengujian bahwa sinyal R-S, sinyal S-T dan sinyal T-R telah bergeser dengan nilai beda fasa masing-masing 120<sup>0</sup> atau 85 hitungan pada kecepatan *clock* 12.8 MHz.

### Referensi

- [1] Tim Contained Energy Indonesia. 2013." Buku Panduan Energi yang Terbarukan". Program Nasional Pemberdayaan Masyarakat.

- [2] Teodorescu, R., Liserre, M., & Rodrigues, P. 2011. "Grdi Converters for Photovoltaic and Power Systems". ISBN: 978-0470-050751-3.

- [3] Samman, F. A., Sadjad, R. S., & Yasin, M. 2015. "Simulasi dan Analisis *Inverter* 3-Fasa dengan Sumber Referensi Tegangan pada Jala-jala PLN". Makassar: ISBN: 987-979-18011-1-9.